アイウェーブはFPGA/ASIC がI/O ピンを介してSDカードにアクセスできるSD ホスト・コントローラIPコアを提供します。

このIPコアはSD ホスト・コントローラ標準仕様Version 3.0に準拠し、標準化された実装によりホストシステム及びドライバ設計を単純化しており、製品開発時間を短縮します。

SDメモリーカードをコントロールするため標準レジスタ・セットを持ち、最大104MBPS のデータレートによる超高速(UHS-I)モードをサポートしています。

このSD ホスト・コントローラIPコアは、SD標準ホストシステムとメモリーカード間の高速データ送信を実現するため最新のアドバンスト・ダイレクト・メモリ・アクセス(ADMA2)機能を備えています。

SD送信データはハードウエア制御が大部分であるためCPU仕様に依存しません。

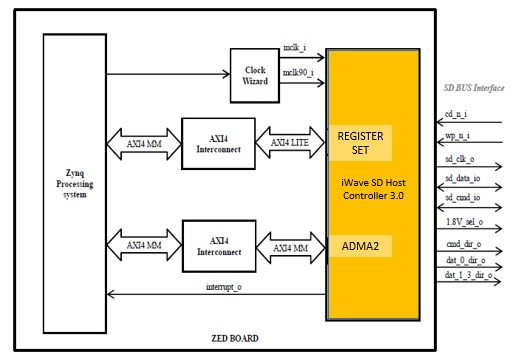

ホスト・コントローラにはシステム側のインターフェイスとSDバス・インターフェイスの二つのインターフェイスがあります。

システム側のインターフェイスはAXI4インターフェイスであり、IPコアはシステムの他の部分と容易にインテグレートできます。

ホスト・コントローラの主な仕様:

・ SD ホスト・コントローラ標準仕様Version 3.0に準拠

・ SD 物理層仕様Version 3.0に準拠

・ 1-bit、4-bit SD モードをサポート

・ SD カード検知入力ピンをサポート

・ SDカード書き込み入力ピンをサポート

・ SDカードへのプログラマブル・クロック周波数生成をサポート

・ 割り込み及びADMA2送信オペレーションをサポート

・ 読み取り、書き込み用に各2Kbyteのデータ・バッファ

・ コマンド、データ用の周期的冗長検査(CRC).

・ レスポンス、データ、CRCトークン&ビジーのタイムアウトモニタリングをサポート

・ 最大2Kbyte のブロック長をサポート

・ シングル・ブロック及びマルチ・ブロック両方のデータ送信をサポート

・ ホスト・プロセッサへの32-bit AXI4メモリ・マップ方式のインターフェイスをサポート

・ SDホスト・コントローラへの32-bit AXI4 Liteインターフェイスをサポート.

・ UHS-I モードサポートクロック状態の自動検知機能があり、エラーが検知されると代替の

内部クロック・ソースが機能します。

・ SDR50及びSDR104モードのチューニングサポート

・ 3.3V ~1.8V スイッチをサポート

・ SDR12、SDR25、SDR50、DDR 50、SDR104モードをサポート

・ 最大データレート: 104MBPS

IPバリデーション:

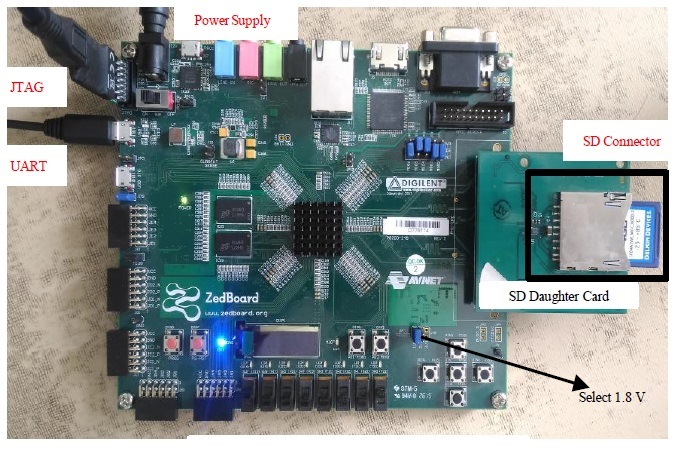

SDR12、SDR25、SDR50、DDR 50及びSDR104モードのIPバリデーションは Xilinx ZED ボードで行っています。

アイウェーブはレファレンス設計及びこのIPをテストするためのSD Linux プラットフォーム・ドライバを提供します。

XILINX ZEDボード

IPの納入物:

・ 設計書

・ RTLコードまたはデバイスのネットリスト

・ IPユーザガイド

・ アイウェーブのSD Linuxプラットフォーム・ドライバ |