IP Core Interface PCIe-ISAブリッジ iWBU104B

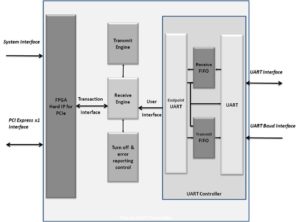

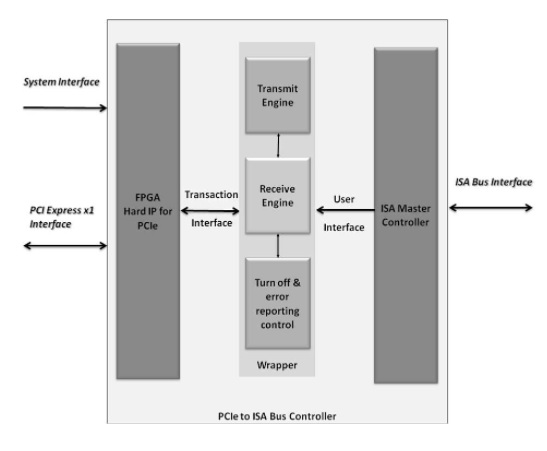

PCIe-ISAブリッジはPCIeをISAマスターバスインターフェイスに変換するIPコアです。

異なったFPGAベンダーのPCIe Hard IPと互換

産業用または組み込み用アプリケーションでの使用が容易な形状

用途:

PC104 busを迅速に接続可能

LPC bus に迅速に接続可能

産業用または組み込み用アプリケーションでの使用

PC用マザーボードへの組み込み

iW-Pcie-to-Isa-bus-controller-Datasheet R1.0

主な仕様

システム インターフェイス:

PCI express インターフェイスと同期した100MHz 外部参照クロック

外部active low reset signalとのインターフェイスをサポート

PCIe インターフェイス:

PCI Express base spec. v1.1に準拠

レーン幅 x1 をサポート

リンク速度 2.5 Gbps をサポート

ユーザーインターフェイス幅 32-bit をサポート

PCIe Express Application インターフェイス:

ターゲットのみをサポート

ISA I/O bus accessの BAR0 をサポート

ISA memory bus accessの memory BAR1 をサポート

ISA Master インターフェイス:

UART ブリッジは16 bit データインターフェイスを実装

ISA インターフェイスのBus clock 8 MHz をサポート

20-bit system address lines をサポート

ラッチ可能なアドレスライン

- システム インターフェイス:

- PCI express インターフェイスと同期した100MHz 外部参照クロック

- 外部active low reset signalとのインターフェイスをサポート

- PCIExpressインターフェイスの同期クロッキング用の100MHz外部基準クロック

- 外部アクティブローリセット信号へのインターフェースをサポート

- PCIExpressインターフェース

- PCIExpress基本仕様v1.1に準拠

- サポートされているレーン幅 x 1

- サポートされているリンク速度 2.5Gbps

- サポートされているユーザーインターフェイスの幅 32ビット

- PCIExpressアプリケーションインターフェイス

- ターゲットのみサポート

- ISA I / OバスアクセスでサポートされるI / O BAR0

- ISAメモリバスアクセスでサポートされるメモリBAR1

- ISAマスターインターフェイス

- ISAブリッジは16ビットデータインターフェイスを実装

- ISAインターフェース用に8MHzのバスクロックをサポート

- バスアドレスラッチイネーブル信号の立ち下がりエッジにラッチできる20ビットシステムアドレスライントライステートをサポート

- ラッチ可能なアドレスラインをサポートし、これらのラッチされていないアドレス信号は、システムに最大16MBのアドレス機能を提供

iW-PCIe-ISA ブリッジ パンフレット 英語版(PDF)

iW-PCIe-ISA ブリッジ 技術仕様 英語版(PDF)